- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Hvad er processen med SiC epitaksial?

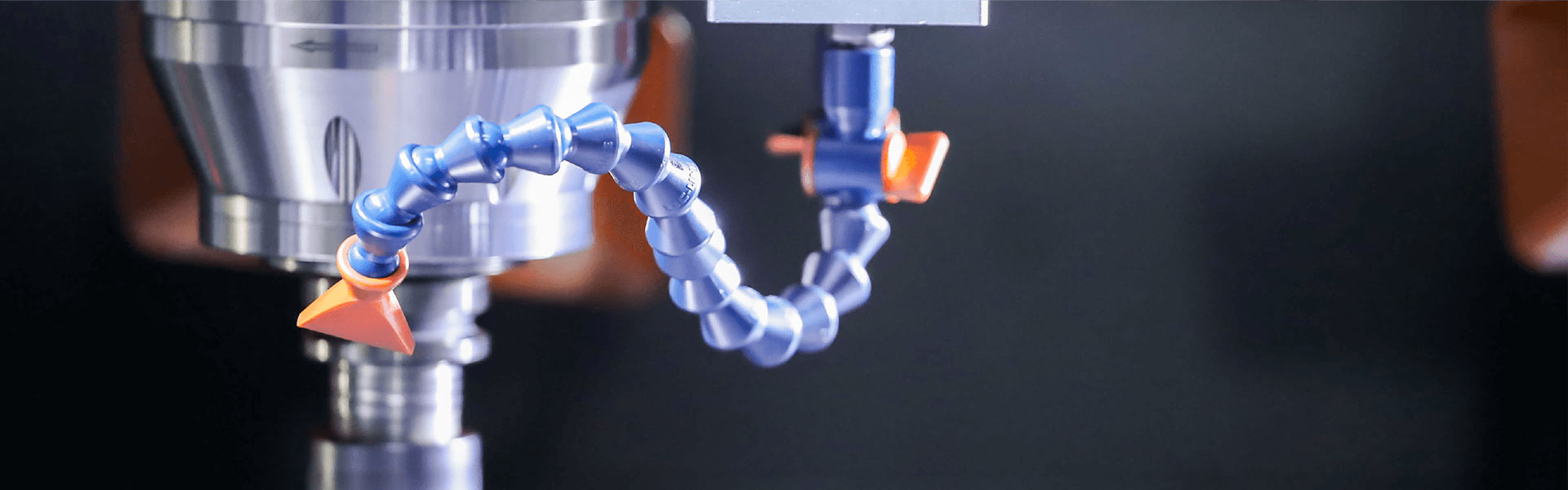

I højspændingsfeltet, især for højspændingsenheder over 20.000V, erSiC epitaksialteknologien står stadig over for flere udfordringer. En af de største vanskeligheder er at opnå høj ensartethed, tykkelse og dopingkoncentration i det epitaksiale lag. Til fremstilling af sådanne højspændingsanordninger kræves en 200um tyk epitaksial siliciumcarbidwafer med fremragende ensartethed og koncentration.

Ved fremstilling af tykke SiC-film til højspændingsenheder kan der dog opstå adskillige defekter, især trekantede defekter. Disse defekter kan have en negativ indvirkning på forberedelsen af højstrømsapparater. Især når store arealchips bruges til at generere høje strømme, reduceres levetiden for minoritetsbærere (såsom elektroner eller huller) betydeligt. Denne reduktion i bærerens levetid kan være problematisk for at opnå den ønskede fremadgående strøm i bipolære enheder, som almindeligvis anvendes i højspændingsapplikationer. For at opnå den ønskede fremadgående strøm i disse enheder skal minoritetsbærerens levetid være mindst 5 mikrosekunder eller længere. Imidlertid er den typiske minoritetsbærerlevetidsparameter forSiC epitaksialwafers er omkring 1 til 2 mikrosekunder.

Derfor, selvomSiC epitaksialprocessen har nået modenhed og kan opfylde kravene til lav- og mellemspændingsapplikationer, yderligere fremskridt og tekniske behandlinger er nødvendige for at overvinde udfordringerne i højspændingsapplikationer. Forbedringer i ensartetheden af tykkelse og dopingkoncentration, reduktion af trekantede defekter og forbedring af minoritetsbærerens levetid er områder, der kræver opmærksomhed og udvikling for at muliggøre en vellykket implementering af SiC epitaksial teknologi i højspændingsenheder.